Advanced Microcontroller Bus Architecture(AMBA)

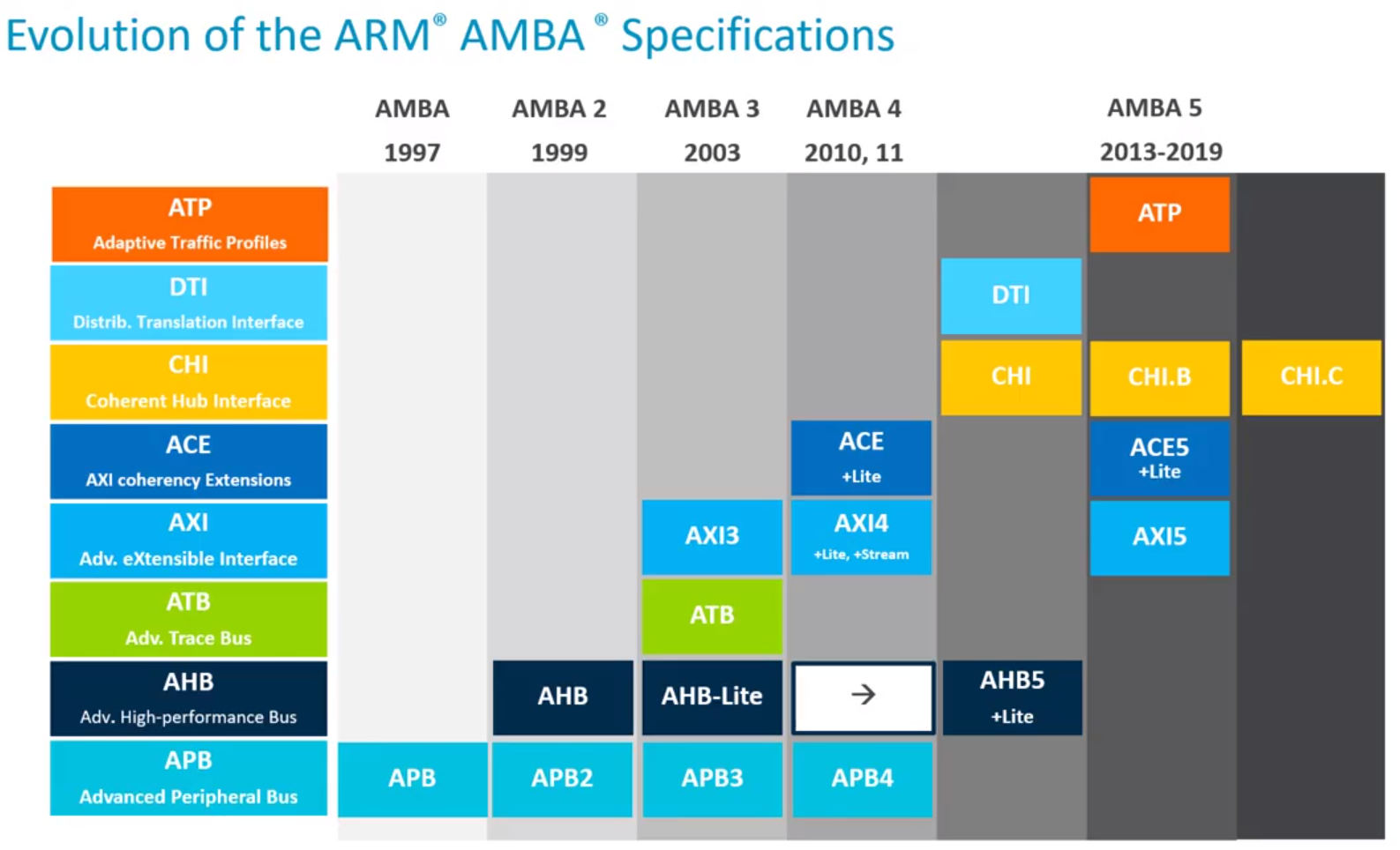

2024-01-17 AMBA 5 is the latest generation of the freely available

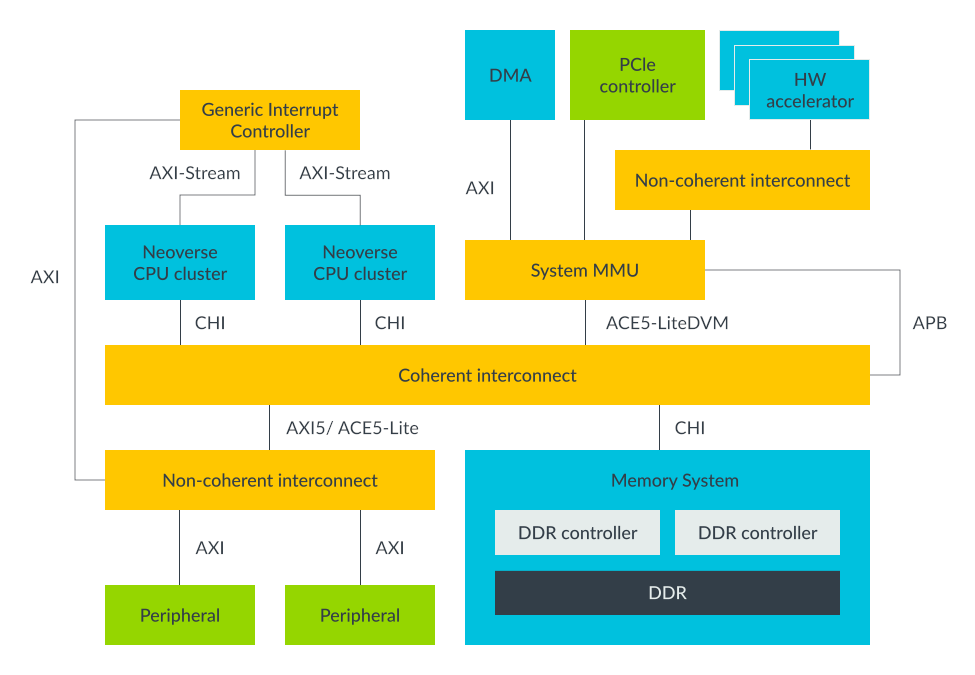

AMBA protocol specifications. It introduces theCoherent Hub Interface(CHI) architecture, which defines the interfaces to connect fully coherent processors and high-performance interconnects. AMBA 5 also introduces the AXI5, ACE5 and AHB5 protocols, which extend prior generations to include a number of performances and scalability features, and to align and complement CHI.

AMBA 5 Protocols

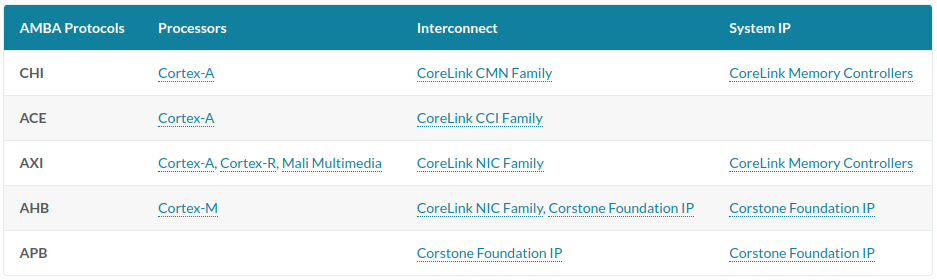

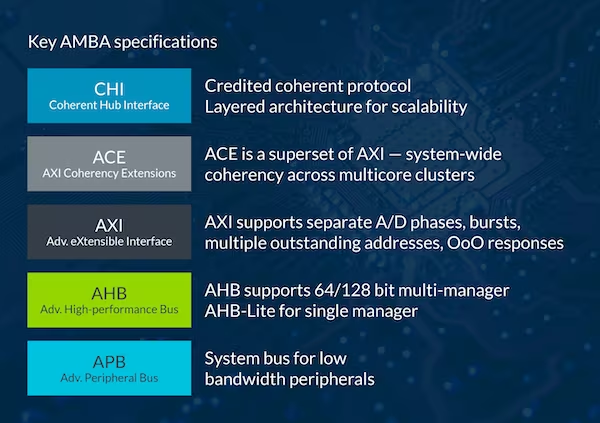

- Coherent Hub Interface (CHI): defines the interfaces to connect fully coherent processors.

- Advanced eXtensible Interface (AXI) and AXI Coherency Extension (ACE): defines the protocols to implement high-frequency, high-bandwidth interconnect designs across a wide range of applications, including mobile, consumer, networking, automotive, and embedded.

- Advanced High-performance Bus (AHB): defines an interface protocol most widely used with Cortex-M processors, for embedded designs and other low latency SoCs.

- Advanced Peripheral Bus (APB): highly compact and low power, it allows configuration and low bandwidth traffic to be isolated from high-performance interconnects. APB supports the low-bandwidth transactions required to access configuration registers and low-bandwidth data traffic in peripherals.

- Advanced Trace Bus (ATB): a data-agnostic interface for transferring trace information between components in a trace system.

- AXI-Stream: defines an interface for unidirectional data transfers with greatly reduced signal routing.

- Credited eXtensible Stream (CXS): defines a credited, non-blocking streaming interface protocol, used in point-to-point packetized communications.

- Adaptive Traffic Profiles (ATP): a synthetic traffic framework capable of modeling systems’ transmitter and receiver high-level memory access behavior in a concise, simple, and portable way.

- Distributed Translation Interface (DTI): aligns with the Arm System MMU architecture, to define a scalable, distributed messaging protocol for translation services.

- Local Translation Interface (LTI): aligns with the Arm System MMU architecture and complements AMBA DTI to improve performance and efficiency for translation services. LTI is a point-to-point protocol and defines the communication between an I/O device and a TBU. It enables devices to directly request a translation for each transaction, while leaving the TBU to manage the TLB. This enables translations to be requested before ordering requirements are met and avoids the need to pass transactions through the TBU. The result is improved performance and reduced silicon area.

- Low Power Interface (LPI): defines Q-Channel and P-Channel interfaces, designed to manage clock and power features of SoC components.

Reference: